两周速通计组课设(报告版)

一、实验目的

完成一个较简单的模型机(计算机主机系统)的设计,加深对微程序控制的计算机主机的基本构成,部件设计,部件间的连接,用户程序及微程序的编制与调试等全过程的体验和认识。所设计的模型机应具备如下能力:

在自行设计的模型机指令集基础上,运行简单用户程序,通过微程序实现对相应硬件的控制,实现模型机的特定功能。

二、课程设计步骤

拟定指令系统

指令格式

内存容量为256×8,基本字长8 位

单字长指令:指令由高 4 位操作码、低 4 位全 0 构成。

双字长指令:指令由第一字节高 4 位操作码、低 4 位为寄存器组操作码;第二字节由操作数、操作数地址、偏移量等构成。

两种指令格式的高四位为操作码,支持 16 种不同的指令。

指令类型

从操作数个数角度:单操作数指令、双操作数指令和无操作数指令。

从数据传送的角度:

RS型: 寄存器 <=> 存储单元 ;

RR型:寄存器 <=> 寄存器

寻址方式

立即数寻址:操作数在指令的第二个字节。如机器指令中的溢出标志存储指令,其溢出标记等就存储在后面相邻的字节中。再如 JX 指令,偏移量就存在下一个字节中。

直接寻址:操作数的地址在指令的第二个字节。如 LOAD 指令,其下一个字节为对应的操作数地址。

指令集

| 指令 | 指令功能 |

|---|---|

| LOAD R0 A1 | 读内存将 A1 地址的数存入寄存器 R0 |

| ADD R | 将ACC、R 中的数相加,结果存入 R0(ACC) |

| SUB R | 将ACC、R中的数相减,结果存入R0(ACC) |

| MOVOUT R | 将ACC中的数移入寄存器R |

| MOVIN R | 将寄存器R中的数移入ACC |

| STORE A2 | 将ACC 所保存的计算结果存到内存地址 A2 |

| JMP A3 | 根据ACC中的数是否满足X字段的条件决定是否跳转到第二字节中的地址A3 |

| HALT | 停机 |

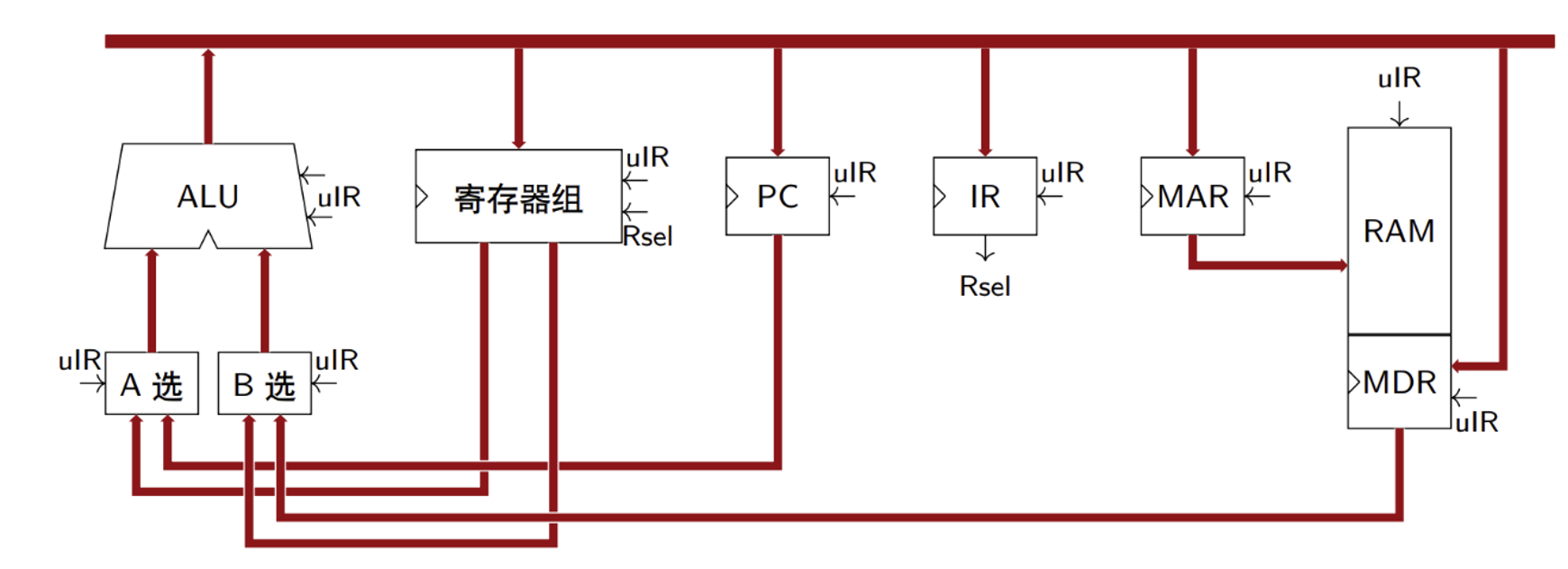

总体结构与数据通路

总体结构

总体结构的设计参考课件中的设计方案,下面简要介绍各个部分

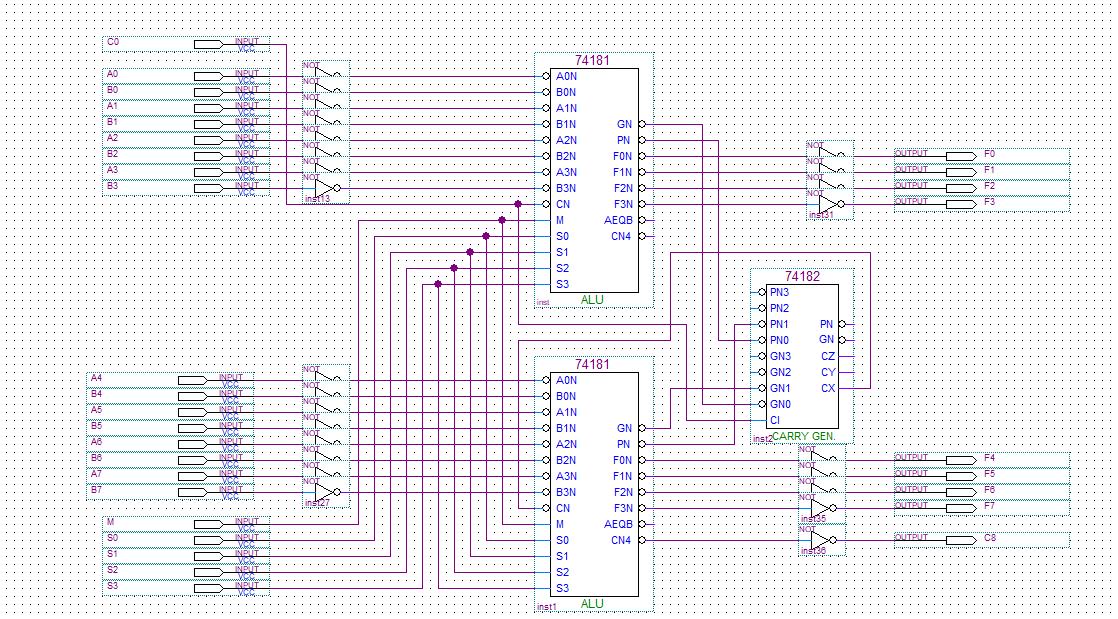

ALU

采用8位并行超前进位运算器

寄存器

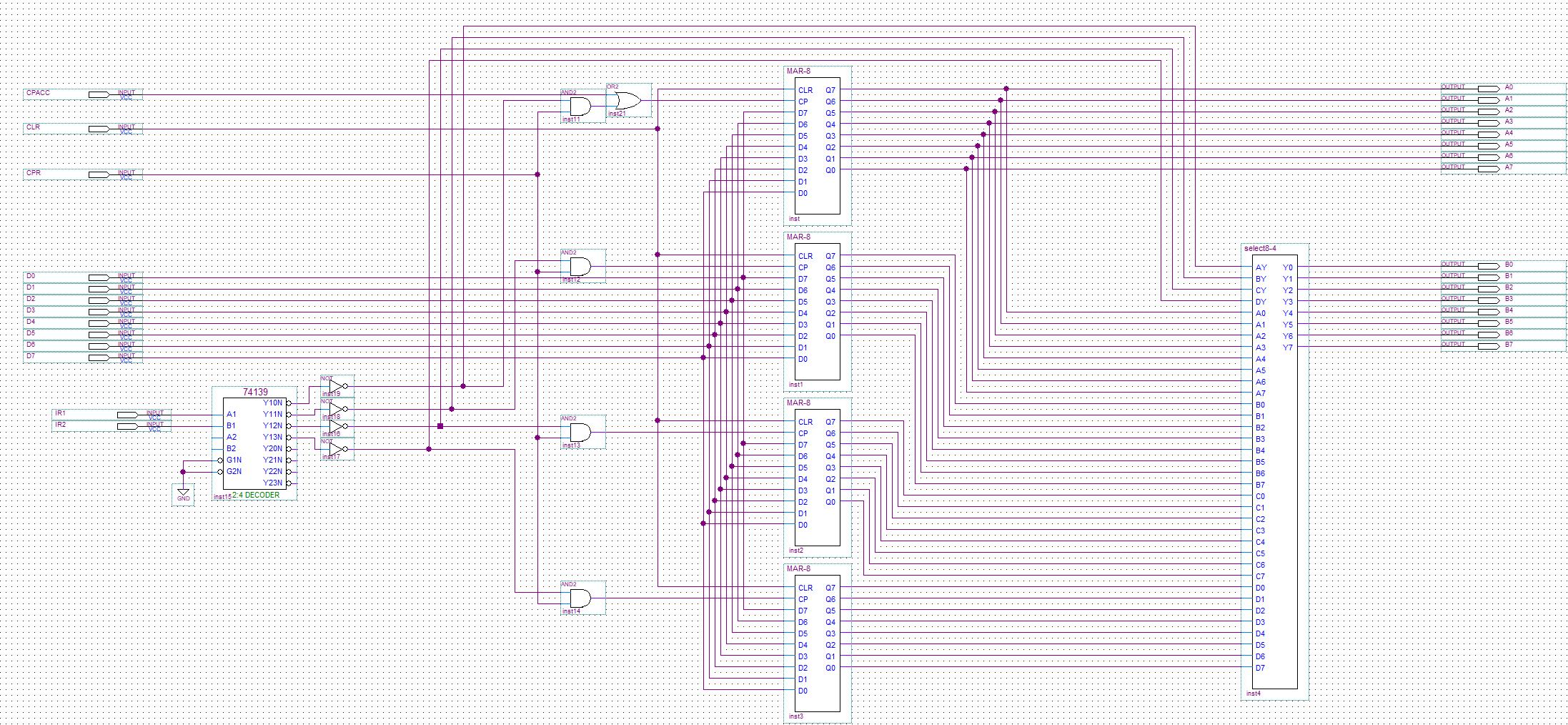

- 通用寄存器组:核心是四片八位寄存器,输入输出端采用二四译码器进行片选,同时输出端使用一片四选一选择器进行数据输出控制。R0寄存器作为选择器A的数据来源,四片寄存器的数据可以作为选择器 B 任意一个的数据来源。

- IR作为指令寄存器,拥有8位字长

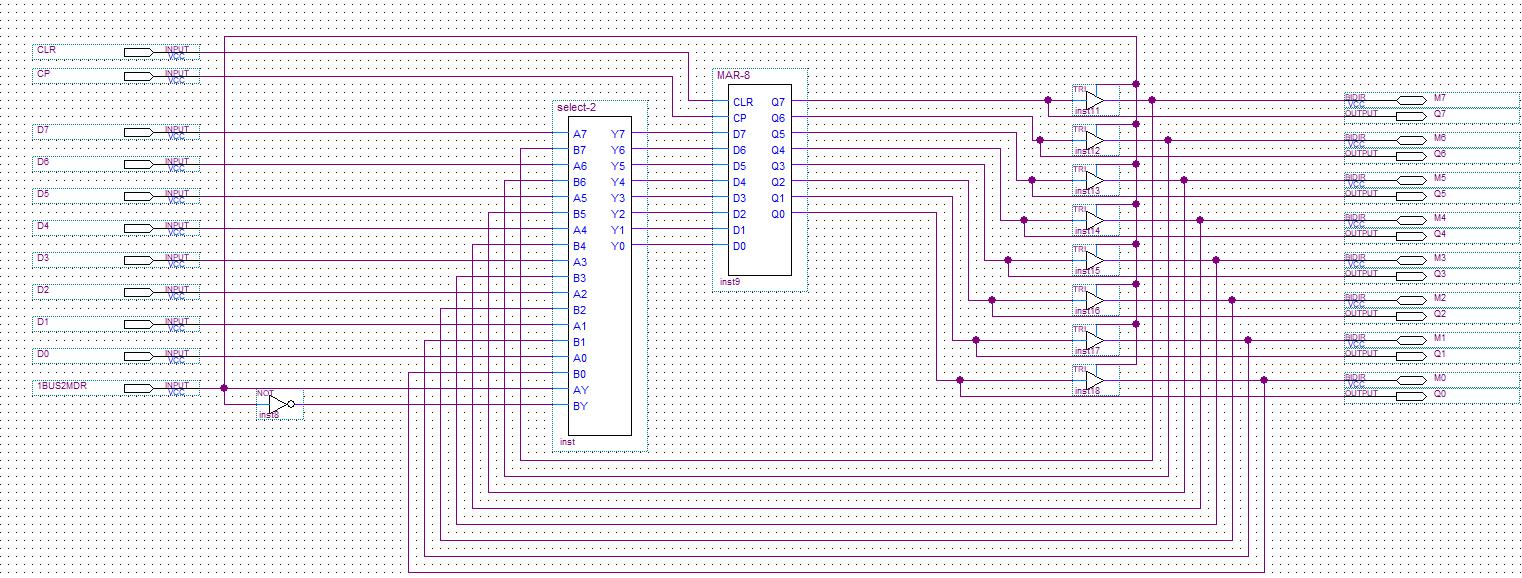

- MAR为地址寄存器,8位

- MDR为数据寄存器,8位

选择器

A选择器:数据来源是PC和ACC

B选择器:数据来源是MDR和通用寄存器组中某一被指定的寄存器的输出数据

微地址形成部件中的选择器:

输出端链接μPC,数据来源为IR的高四位操作码,此时低四位置零,用于QJP指令按操作码转移;也可根据IR的X字段,其余位置零,用于XJP指令,跳转到对应寻址周期;亦可根据跳转指令JMP,通过判断条件是否成立,选择顺序执行或跳转到目标地址;以及JP无条件转移到取值周期

数据通路

模型机的数据通路是以总线为基础,以ALU为核心构成,下面就机器指令分析其数据通路

取指

(PC) -> BUS -> MAR

(PC) +1 -> PC

(RAM) -> MDR -> BUS -> IR

LOAD

(PC) -> BUS -> MAR

(PC) +1 -> PC

(RAM) -> MDR -> BUS -> MAR

(RAM) -> MDR -> BUS -> R0

ADD R

(R0) + (R) -> BUS -> R0

SUB

(R0) - (R) -> BUS -> R0

STORE

(PC) -> BUS -> MAR

(PC) +1 -> PC

(RAM) -> MDR -> BUS -> MAR

(R0) -> BUS -> MDR -> RAM

确定控制方式

采用微程序方式,微程序的执行方式采用增量方式

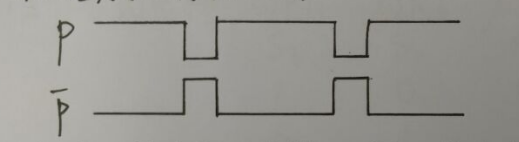

微程序控制器时序

P脉冲的低电平 用作控制存储器读命令$$μ\overline{RD}$$,P脉冲的上升沿将读出的微指令送给μIR;

$$\overline{P}$$脉冲上升沿将形成的后继地址送给微程序计数器μPC,同时将运算结果送入指定的寄存器

微指令格式

微指令字长24位,即$$μIR_{23} — μIR_0$$ ,下面是微指令字段定义

A选择器控制

| $$μIR_{23}$$ | $$μIR_{22}$$ | |

|---|---|---|

| 0 | 0 | 备用 |

| 0 | 1 | ACC_A |

| 1 | 0 | PC_A |

| 1 | 1 | 备用 |

B选择器控制

| $$μIR_{21}$$ | $$μIR_{20}$$ | |

|---|---|---|

| 0 | 0 | 备用 |

| 0 | 1 | MDR_B |

| 1 | 0 | R_B |

| 1 | 1 | 备用 |

ALU工作方式选择

| $$μIR_{19}$$ $$S_3$$ | $$μIR_{18}$$ $$S_2$$ | $$μIR_{17}$$ $$S_1$$ | $$μIR_{16}$$ $$S_0$$ | |

|---|---|---|---|---|

| 1 | 0 | 0 | 1 | 加法 |

| 0 | 1 | 1 | 0 | 减法 |

初始进位控制

| $$μIR_{15}$$ | |

|---|---|

| 0 | C0 = 0 |

| 1 | C1 = 1 |

寄存器打入脉冲分配

| $$μIR_{14}$$ | $$μIR_{13}$$ | $$μIR_{12}$$ | |

|---|---|---|---|

| 1 | 1 | 0 | CPACC |

| 1 | 0 | 1 | CPR |

| 1 | 0 | 0 | CPPC |

| 0 | 1 | 1 | CPIR |

| 0 | 1 | 0 | CPMAR |

| 0 | 0 | 1 | CPMDR |

内存访问控制

| $$μIR_{11}$$ | $$μIR_{10}$$ | |

|---|---|---|

| 1 | 0 | $$\overline{RD}$$ |

| 0 | 1 | $$\overline{WR}$$ |

MDR三态输入控制

| $$μIR_9$$ | |

|---|---|

| 0 | 总线数据直接输入 |

| 1 | RAM端数据输入 |

停机控制HLT

| $$μIR_8$$ | |

|---|---|

| 0 | 不停机 |

| 1 | 停机 |

后继微地址形成方式

| $$μIR_2$$ | $$μIR_1$$ | $$μIR_0$$ | |

|---|---|---|---|

| 0 | 0 | 1 | μPC + 1 顺序执行 |

| 0 | 1 | 0 | JP 无条件转移至取指周期 |

| 0 | 1 | 1 | QJP 按操作码转移 |

| 1 | 0 | 0 | XJP 按X字段转移至对应寻址周期 |

| 1 | 0 | 1 | JJP 跳转至第二字节地址 |

指令执行流程

- 微程序从00H处取指开始执行,将指令送入IR,并使PC +1

- 取指周期结束后,根据指令0000X00中的X字段,进入对应的间址周期

- IR的高四位作为OP,同时作为指令在微程序中对应的首地址。取指和间址周期结束后,跳转至X0H,此处X为OP;

- 指令对应的微程序执行,在执行结束后,使PC指向下一条指令对应的ROM地址,并使μPC跳转至00H,进入取指周期

- 增城顺序执行微指令时,后继微地址形成位为“μPC+1“

拓展部分的实现说明

本次实验共计完成了两级拓展,说明如下:

一级拓展要求实现多种寻址方式以及跳转指令,主要功能由硬件实现,在指令中取中间两位作为X字段,以表示四种寻址方式以及四种转移条件,同时新增两种后继微地址形成方式,分别为XJP和JJP。

XJP指令执行时,若指令X字段为00,则将00H打入μPC,进行取指操作;否则,将除X字段其他位置零后打入μPC,转移至对应寻址周期。

JJP指令执行时,若指令X字段为11,则默认无条件转移,否则,先根据ACC中储存数据是否符合对应条件,来决定是否需要转移,若条件不成立,则让μPC+1,否则进行取指操作。

三、系统的调试、测试方法

单元测试部分

寄存器组测试

D0-D7、P、CPR、CPACC、CLR、AC1、IR1、IR2接开关作为输入,A0-A7、B0-B7 接指示灯。通过控制开关查看将不同数字存进不同寄存器组的情况,并在存放后检查不同寄存器组的输出情况,着重关注 IR1、IR2 对于输入输出的控制方式是否与预期相符。

软件自带 2-4 译码器测试

PPT 上推荐可以使用软件自带的 74139 组件作为 2-4 译码器使用,由于不能确定 A1、A2、B1、B2 的关系以及输出情况,特对 74139 进行测试。将 A1、A2、B1、B2 接开关作为输入,所有 YN 端接指示灯作为输出。通过调整 A、B 的输入,观察指示灯的输出,最后确认 A1、B1 控制是一对译码输入,A2、B2 是一对译码输入,译码的输出是 3 个 1 和 1 个 0。

累加器测试

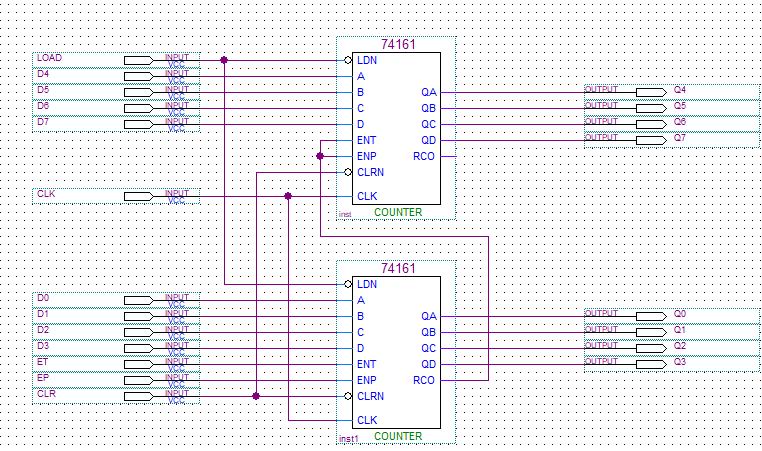

D0-D7、LD 接开关作为输入,CK 接单脉冲,Q0-Q7 接指示灯。通过控制开关和单脉冲,观察指示灯闪烁情况,分别验证累加器的自增加一、置数功能。

ALU 测试

A、B 输入、CN、M、S0-S3 接开关,F 输出和 CN4 接指示灯。通过控制开关,观察指示灯闪烁情况,分别验证 ALU 加法、减法、直传功能,并观察 CN4的进位情况。

整机测试部分

- 指令经过检查无误后,通过软件以十六进制的形式写入 RAM 的相应单元。

- 微程序经过检查无误后,通过软件以十六进制的形式写入 ROM 的相应单元。

- 拨清零开关使所有寄存器、累加器清零,按复位键。

- 不断点击单脉冲,每次点击后观察 ROM 的当前微指令值,并根据提前连接的指示灯观察 MDR、AB选择器、MAR、IR、μPC的输出情况。

- 运行到停机指令后通过软件读取 RAM 的值,验证结果。

- 单脉冲确保运行结果无误后,将单脉冲替换为连续脉冲,并将所有指示灯断开连接,以免影响连续脉冲。

- 按一次脉冲键发单脉冲使启动器发送连续脉冲,开始运行程序。

- 等到程序运行结束后通过软件读取 RAM 的值,验证结果。

遇到的问题和解决方案

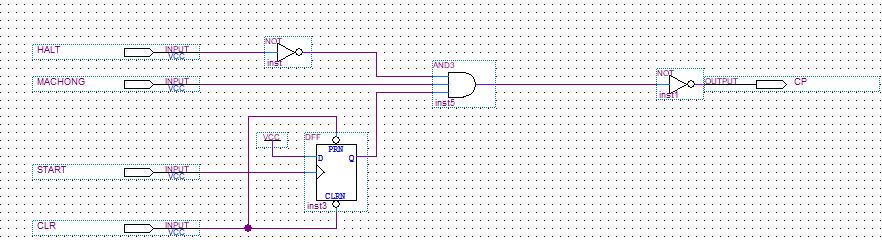

连续脉冲运行紊乱问题

使用连续脉冲运行,会发生加法结果错误,寄存器无法存数、读写内存等问题,而单脉冲则不会出现上述问题

在实验老师的提醒下,去除调试用LED灯后仍未起效,在启停电路出口添加T触发器后成功解决。

小组成员分工

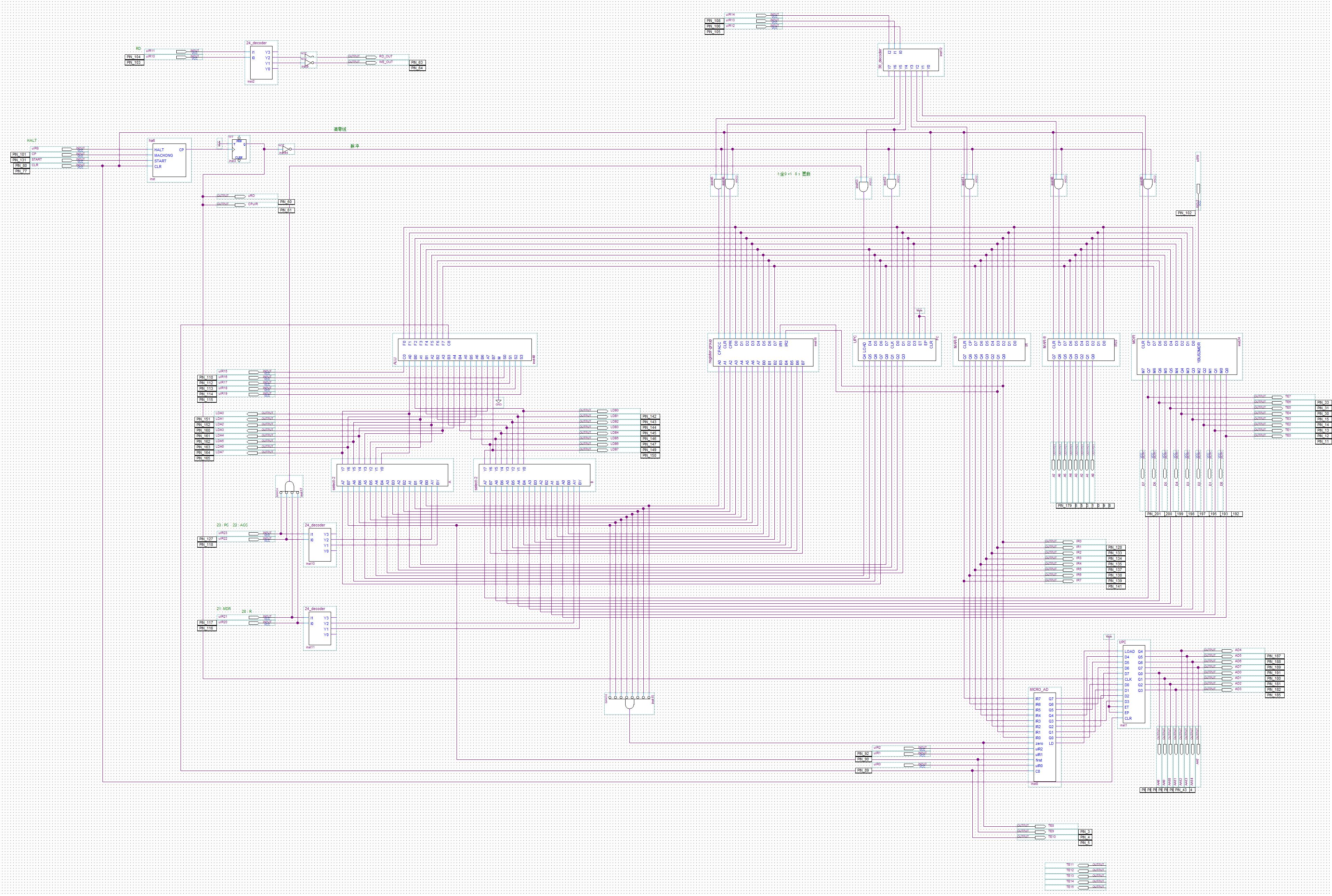

成员1

绘制通用寄存器组、MDR、选择器等基础组件,绘制外部数据总通路,绘制部分微地址形成部件、通过实验台调试模型机,修复错误

成员2

微指令及调试程序设计和编码,绘制部分微地址形成部件,通过实验台调试模型机,修复错误

课程设计总结

- 通过动手设计简单模型机,加深对微程序控制的计算机构成、设计、部件连接、程序设计与调试全过程的理解

- 通过实验台调试任务,加强实践中解决工程问题的能力,培养了团队协作意识与能力,掌握排查错误的能力

- 在设计中额外学习了Excel公式、制表技能,通过Git管理模型机及组件,提升计算机方面的其他能力

- 总线结构有利也有弊,好处在于电路结构清晰、数据通路简单、组合多样,弊端在于容易发生读写冲突、总线上只能传输一组数据。

- 通过与队友的沟通交流发现、弥补了自己在一些知识上的欠缺,也使我团队协作能力有了进一步提升。

附录

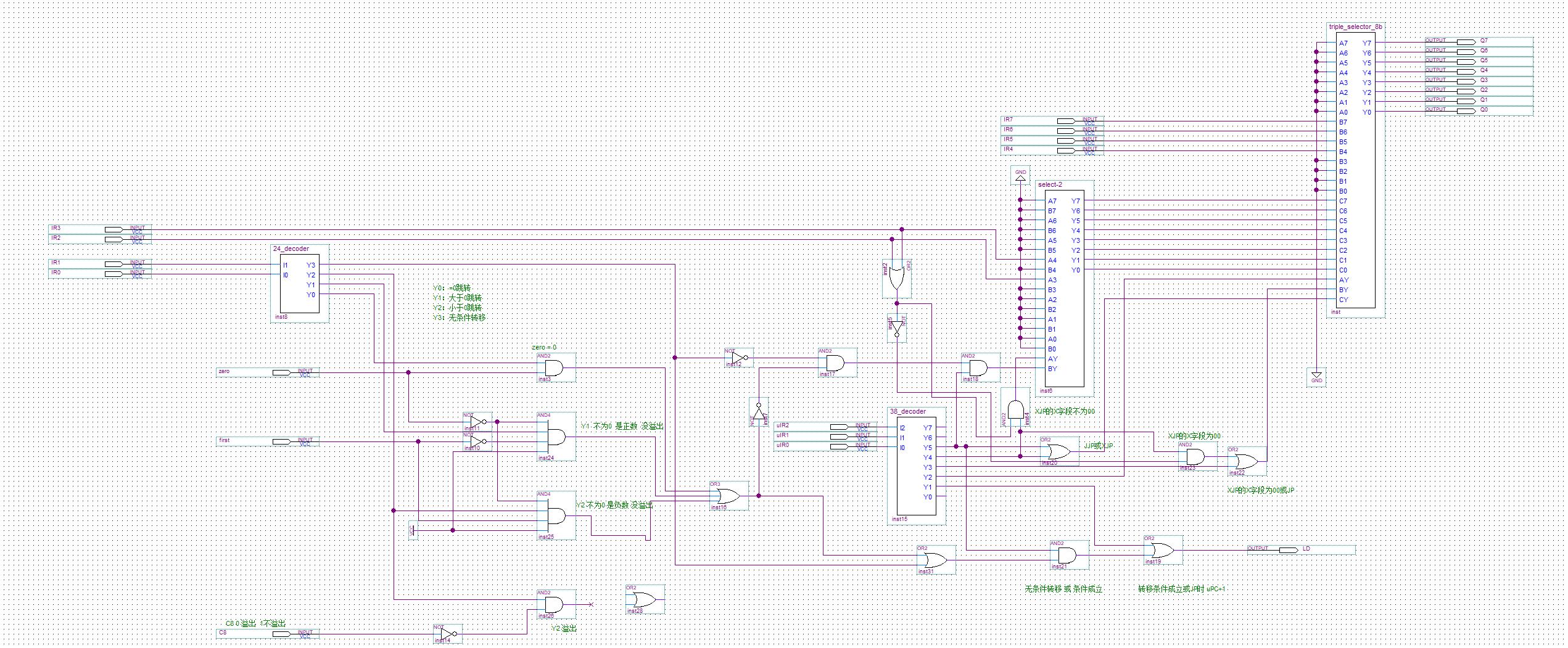

附录一 各器件图与总体结构图

总体结构图

ALU

寄存器组

MDR

带置数功能的计数器

启停电路

微地址形成部件

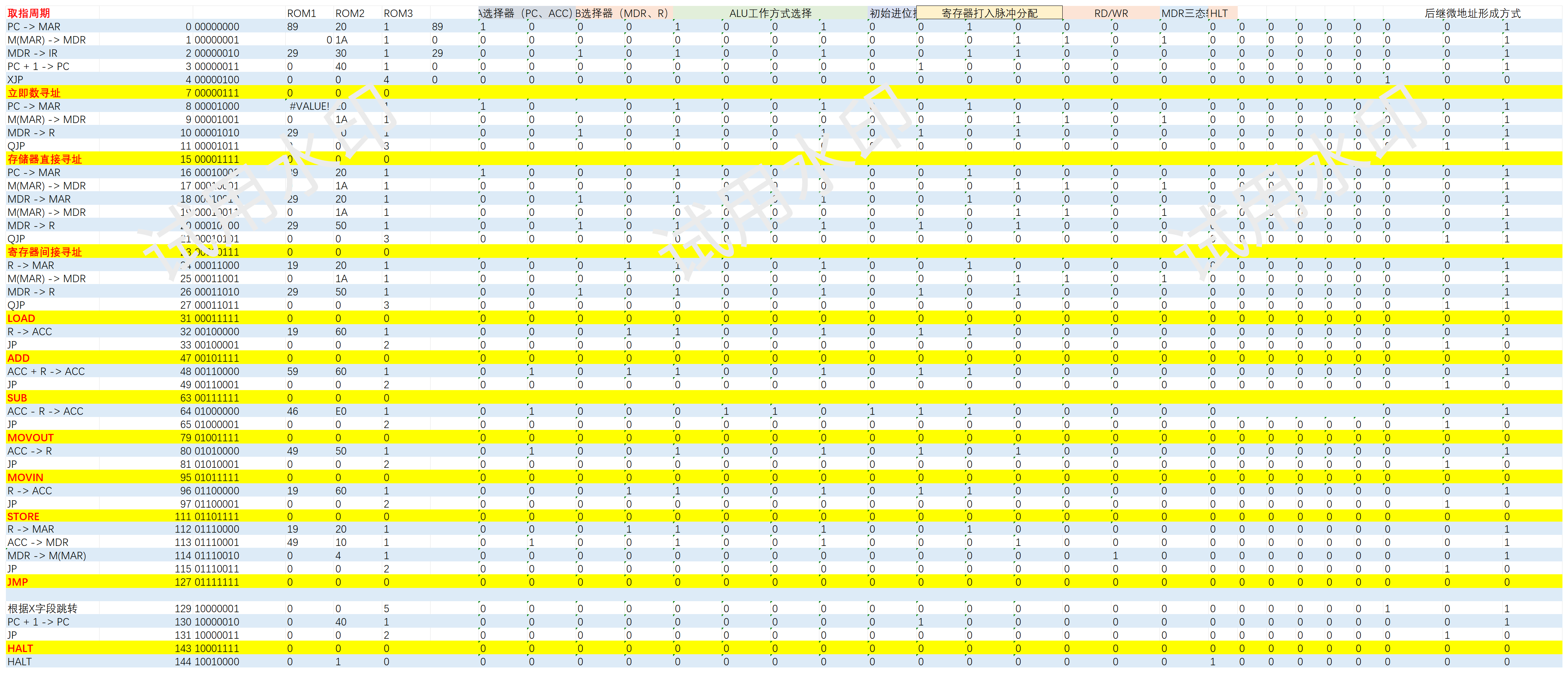

附录二 微程序编码

附录三 调试程序

基础

| 地址 | 机器指令 | 指令值 | 十六进制格式 |

|---|---|---|---|

| 00 | load 40h | 0010 1000 | 28 |

| 01 | 0100 0000 | 40 | |

| 02 | movout r2 | 0101 0010 | 52 |

| 03 | load 41h | 0010 1000 | 28 |

| 04 | 0100 0001 | 41 | |

| 05 | movout r3 | 0101 0011 | 53 |

| 06 | load | 0010 1100 | 2C |

| 07 | movout r1 | 0101 0001 | 51 |

| 08 | movin r2 | 0110 0010 | 62 |

| 09 | movout r3 | 0101 0011 | 53 |

| 0A | load | 0010 1100 | 2C |

| 0B | add r1 | 0011 0001 | 31 |

| 0C | store r2 | 0111 0010 | 73 |

| 0D | halt | 1001 0000 | 90 |

| …… | |||

| 36 | 操作数1 | F0 | |

| 37 | 操作数2 | 07 | |

| …… | |||

| 40 | 地址1 | 36 | |

| 41 | 地址2 | 37 |

一级拓展

| 地址 | 机器指令 | 指令值 | 十六进制格式 |

|---|---|---|---|

| 00 | load 40h | 0010 1001 | 29 |

| 01 | 0100 0000 | 40 | |

| 02 | movout r1 | 0101 0001 | 51 |

| 03 | load 41h | 0010 1010 | 2A |

| 04 | 0100 0001 | 41 | |

| 05 | movout r2 | 0101 0010 | 52 |

| 06 | load (r2) | 0010 1110 | 2E |

| 07 | movout r3 | 0101 0011 | 53 |

| 08 | load r1 | 0010 1101 | 2D |

| 09 | movout r2 | 0101 0010 | 52 |

| 0A | sub r3 | 0100 0011 | 43 |

| 0B | jmp >0 | 1000 0001 | 81 |

| 0C | 跳转地址 | 13 | |

| 0D | movin r2 | 0110 0010 | 62 |

| 0E | store 41h | 0111 1001 | 79 |

| 0F | 41h | 0100 0001 | 41 |

| 10 | movin r3 | 0110 0011 | 63 |

| 11 | store 40h | 0111 1001 | 79 |

| 12 | 40h | 0100 0000 | 40 |

| 13 | halt | 1001 0000 | 90 |

二级拓展

| 地址 | 机器指令 | 指令值 | 十六进制格式 |

|---|---|---|---|

| 00 | load 80h | 0010 1000 | 28 |

| 01 | 80h | 80 | |

| 02 | movout r1 | 0101 0001 | 51 |

| 03 | load r0 | 0010 1100 | 2C |

| 04 | add r2 | 0011 0010 | 32 |

| 05 | movout r2 | 0101 0010 | 52 |

| 06 | add r1+1 | 1010 0001 | A1 |

| 07 | load | 0010 1100 | 2C |

| 08 | jmp >0 | 1000 0001 | 81 |

| 09 | 循环开始地址 | ||

| 0A | jmp <0 | 1000 0010 | 82 |

| 0B | 循环开始地址 | ||

| 0C | movin r2 | 0110 0010 | 62 |

| 0D | store 81h | 0111 0101 | 75 |

| 0E | 81h | 81 | |

| 0F | halt | 1001 0000 | 90 |